|

|

|

|

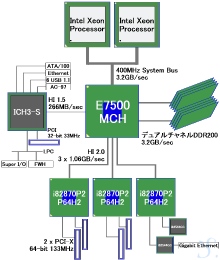

Intel E7500, E7501 chipset

クリックで拡大

| |

Intel E7500は、Socket603 Xeonプロセッサをサポートするワークステーションおよびサーバー向けのMCH。

PrestoniaコアのXeonプロセッサリリースに合わせて発表され、デュアルプロセッサ構成をサポートする。

メモリはデュアルチャネルのDDR200 ECC Registeredをサポートし、プロセッサバスと同じ3.2GB/secの帯域幅となる。

後に533MHz FSB Xeonに合わせて投入されたE7501では、Socket604及び533MHz FSBと、

DDR266のサポートが追加された。533MHz FSB動作時にはDDR266、400MHz FSB時はDDR200のサポートとなる。

このほか、メモリインターフェースがシングルチャネルで利用可能となっている。

内部バスではIntel Hub Architecture 2.0がサポートされた。HI 2.0のチャネルは1.06GB/sec (16-bit 266MHz/533MHz)

の帯域幅を持ち、3チャネルまで利用できる。これにi82870P2 PCI/PCI-X 64-bit Hub 2 (P64H2) を接続することで、

チャネルごとに2個の独立したPCI-X、システムとしては最大6 PCI-Xバスを備えることが可能となる。

I/OコントローラにはICH3-Sが組み合わせられ、MCHとはHub Interface 1.5で接続する。HI 1.5は、帯域幅など基本的には

HI 1.0と同じものだが、HI 2.0と電気的に互換性を持つ仕様とされている。

|

Specs

| | E7500 | E7501 |

|---|

| チップ名称 | E7500 MCH | E7501 MCH |

| コード名 | Plumas | Plumas 533 |

| プラットフォーム | 2-way Xeon | 2-way Xeon |

| FSB | 400MHz | 533/400MHz |

| メモリインターフェース | 144-bit DDR ECC | 144-bit, 72-bit DDR ECC |

| 対応メモリ | DDR200 ECC Regd. | DDR266/200 ECC Regd. |

| 最大積載メモリ | 16-Bank 16GB | 16-Bank 16GB, 8GB in single-channel mode |

| 統合グラフィックス | - | - |

| AGP | - | - |

| HUBインターフェース | 3 HI 2.0, HI 1.5 | 3 HI 2.0, HI 1.5 |

| バス帯域幅 | 1.06GB/sec, 266MB/sec | 1.06GB/sec, 266MB/sec |

| ICH | ICH3-S | ICH3-S |

| ICH型番 | 82801CA | 82801CA |

| ローカルバス | PCI, PCI-X (P64H2) | PCI, PCI-X (P64H2) |

| IDEチャネル | 2 ATA/100 | 2 ATA/100 |

| USB | 6 USB 1.1 | 6 USB 1.1 |

| IEEE1394 | - | - |

| ネットワーク | 100Mbit Ethernet | 100Mbit Ethernet |

| SMBusコントローラ | 2.0 | 2.0 |

| MCHパッケージ | 1005 FC-BGA | 1005FC-BGA |

| ICHパッケージ | 421 BGA | 421 BGA |

| P64H2パッケージ | 567 FC-BGA | 567 FC-BGA |

| 製造プロセス | - | - |

| 登場時期 | 2002年2月 - 現在 | 2002年11月 - 現在 |

| |

|