Advertisement

Site Navi

Related Links

Advertisement

February, 2004 updated

2004年2月更新

Specs

AMD製プロセッサ - プロセッサスペックノート

目次

- Family 15 8th Generation: Opteron, Athlon 64 FX, Athlon 64

- Family 6 7th Generation: Athlon XP, Athlon MP, Athlon

- Family 5 6th Generation: K6, K6-2, K6-III

AMD Family 15 8th Generation Processors

| Codename | Clock | HT Link | L1/L2/L3 | Memory | Ex. | Process | Trs. | Die size | |

|---|---|---|---|---|---|---|---|---|---|

| Opteron | Athens | - | - | 64+64KB/1MB/- | 2xDDR | SSE2 | 90nm/9 | - | - |

| Troy | - | - | 64+64KB/1MB/- | 2xDDR | SSE2 | 90nm/9 | - | - | |

| Venus | - | - | 64+64KB/1MB/- | 2xDDR | SSE2 | 90nm/9 | - | - | |

| SledgeHammer | 2.4-1.4GHz | 800MHz 16-bit 3 Links | 64+64KB/1MB/- | 2xDDR400/333 | SSE2 | 0.13 | 105.9M | 193sqmm | |

| Athlon 64 FX | San Diego | 2.6GHz | 16-bit 1 Link | 64+64KB/1MB/- | 2xDDR400 | SSE2 | 90nm/9 | - | - |

| SledgeHammer | 2.4-2.2GHz | 800MHz 16-bit 1 Link | 64+64KB/1MB/- | 2xDDR400 | SSE2 | 0.13 | 105.9M | 193sqmm | |

| Athlon 64 | Winchester | 2.6-2.4GHz | 16-bit 1Link | 64+64KB/512KB/- | 2xDDR | SSE2 | 90nm | - | - |

| Newcastle | 2.4-2.2GHz | 1GHz-800MHz 16-bit 1 Link | 64+64KB/512KB/- | 2xDDR400 | SSE2 | 0.13 | - | - | |

| ClawHammer | 2.4-2GHz | 1GHz-800MHz 16-bit 1 Link | 64+64KB/[1MB/512KB]/- | DDR400 | SSE2 | 0.13 | 105.9M | 193sqmm | |

| Athlon XP | Paris | 1.8-1.4GHz | 16-bit 1 Link | 64+64KB/256KB/- | DDR400 | SSE2 | 0.13 | - | - |

| DTR Athlon 64 | Odessa | 16-bit 1 Link | - | -/-/- | - | SSE2 | 90nm | - | - |

| ClawHammer | 2.2-1.8GHz | 800MHz 16-bit 1 Link | 64+64KB/1MB/- | DDR400 | SSE2 | 0.13 | 105.9M | 193sqmm | |

| Mobile Athlon 64 | Oakville | 16-bit 1 Link | - | -/-/- | - | SSE2 | 90nm | - | - |

| ClawHammer | 2-1.6GHz | 800MHz 16-bit 1 Link | 64+64KB/1MB/- | DDR400 | SSE2 | 0.13 | 105.9M | 193sqmm | |

| Mobile Athlon XP-M | Dublin | - | 16-bit 1 Link | 64+64KB/256KB/- | DDR400 | SSE2 | 0.13 | - | - |

AMD Opteronは、AMD64アーキテクチャに基づくサーバー及びワークステーション向けプロセッサとして2003年4月22日に 発表されました。AMD64では、64-bitアプリケーションが実行できるだけでなく、既存の32-bitアプリケーションでも高い性能を発揮するとされます。 また、Opteronではメモリコントローラを内蔵、複数のHyperTransport Technologyリンクの実装によるスケーラブルなマルチプロセッサ環境への 対応といった特徴を持ちます。このほか、Opteronでは整数パイプラインが12ステージと、Athlon XPから2ステージ追加されました。 パイプラインの細分化は、SOIの採用とともにクロックスケールの向上に大きく貢献します。

AMD64ベースのデスクトップ及びモバイル向けプロセッサは、Athlon 64 FX、Athlon 64、DTR Athlon 64の3種類が9月23日に 発表されました。Athlon 64 FXはOpteron 100シリーズと同様にデュアルチャネルDDRメモリに対応、940-pinパッケージを採用しています。 Athlon 64とDTR Athlon 64はシングルチャネルDDRメモリインターフェースを備え、Socket 754に対応しています。これらはいずれも Opteronと同様のアーキテクチャを基としますが、利用できるHyperTransportは1リンクに制限されます。

2004年Q1には新たにSocket 939プラットフォームが登場し、これ以降のAthlon 64 FXとデスクトップ向けAthlon 64は 939-pinパッケージへと移行することになります。Socket 939ではデュアルチャネルメモリをサポートすることと、 Socket 940に比べシステムの価格が抑えられることが主な特徴です。

- AMD64 Architecture - 既存の32-bit x86ソフトウェアとの互換性を保ちつつ64-bitコンピューティングを実現したもので、 K7アーキテクチャをベースに拡張されたと見られます。プロセッサには新たに64-bit ロングモードが備えられ、 主要なレジスタが64-bitに拡張されるとともに、汎用レジスタとSSEレジスタは16個に増加しました

- Integrated DDR DRAM Memory Controller - デュアルチャネルのDDRメモリコントローラを内蔵することで、 メモリアクセスレイテンシを削減しています。 OpteronではDDR333までのメモリに対応、帯域幅は最大5.3GB/secで、プロセッサあたり8 Registered ECC DIMMをサポートし 最大16GBのメモリが利用できます。なお、Athlon 64とAthlon 64 FX、Opteron x48からはDDR400メモリをサポートしました

- HyperTransport Technology - 最高3個までのHyperTransportリンクをサポートし、プロセッサあたり最大19.2GB/secの帯域幅を実現しています。 HyperTransportは片方向16-bit、最高800MHz double-pumpedで利用でき、リンクごとに6.4GB/secの帯域幅を確保できます。 各HyperTransportは緊密に結びついており、それぞれに接続したプロセッサやチップセットを利用することができます

- 256TB of memory address space - 64-bit長のデータパス、アドレスパスにおいて、48-bit/256TBの仮想アドレス空間、 40-bit/1TBの物理アドレス空間をサポート

- Scalable MP - HyperTransportリンクによりユニプロセッサ構成から8-wayマルチプロセッサまで対応できます

- SSE2 support - SSE、 SSE2と完全に互換な全ての拡張命令をサポートします

- 2 additional pipeline stages - パイプラインステージの追加により、性能と動作クロックのスケーラビリティを向上させています

- Higher IPC - 大容量TLB、Flash Filter、アドバンスド分岐予測アルゴリズムなどの採用により、IPCを向上させています

| Brand | Model Number | Package | Operating Voltage | Case Temperature | L2 Cache Size | Part Definition | - |

|---|---|---|---|---|---|---|---|

| OSA | AMD Opteron Server | ||||||

| x40 | 1400MHz | ||||||

| x42 | 1600MHz | ||||||

| x44 | 1800MHz | ||||||

| x46 | 2000MHz | ||||||

| x48 | 2200MHz | ||||||

| x50 | 2400MHz | ||||||

| C | 940-pin Lidded CuPCGA | ||||||

| E | 1.50V | ||||||

| P | 70 'C | ||||||

| 5 | 1MB | ||||||

| AL | Model 5, Dual-Processor, rev. C0 | ||||||

| AK | Model 5, Uni-Processor, rev. C0 | ||||||

| AM | Model 5, (8-way) Multi-Processor, rev. C0 | ||||||

| x40 | 1400MHz | ||||||

| x42 | 1600MHz | ||||||

| x44 | 1800MHz | ||||||

| C | 940-pin Lidded CuPCGA | ||||||

| C | 1.55V | ||||||

| O | 69 'C | ||||||

| 5 | 1MB | ||||||

| AH | Model 5, Dual-Processor, rev. B3 | ||||||

| AG | Model 5, Uni-Processor, rev. B3 | ||||||

| AI | Model 5, (8-way) Multi-Processor, rev. B3 | ||||||

| ADA | AMD Athlon 64 Desktop | ||||||

| FX53 | 2400MHz | ||||||

| - | - | ||||||

| E | 1.50V | ||||||

| P | 70 'C | ||||||

| 5 | 1MB | ||||||

| AT | Model 5, Rev.CG | ||||||

| FX51 | 2200MHz | ||||||

| FX53 | 2400MHz | ||||||

| C | 940-pin Lidded CuPGA | ||||||

| E | 1.50V | ||||||

| P | 70 'C | ||||||

| 5 | 1MB | ||||||

| AK | Model 5, Rev.C0 | ||||||

| AT | Model 5, Rev.CG | ||||||

| ADA | AMD Athlon 64 Desktop | ||||||

| 3400 | 2200MHz | ||||||

| 3700 | 2400MHz | ||||||

| - | - | ||||||

| E | 1.50V | ||||||

| P | 70 'C | ||||||

| 4 | 512KB | ||||||

| AR | Model 4, Rev.CG, P-state transition support, Improved CnQ | ||||||

| 3200 | 2000MHz | ||||||

| 3400 | 2200MHz | ||||||

| 3700 | 2400MHz | ||||||

| A | 754-pin Lidded OuPGA | ||||||

| E | 1.50V | ||||||

| P | 70 'C | ||||||

| 5 | 1MB | ||||||

| AO | Model 4, (ES) | ||||||

| AP | Model 4, Rev.C0, P-state transition support | ||||||

| AR | Model 4, Rev.CG, P-state transition support, Improved CnQ | ||||||

| 3000 | 2000MHz | ||||||

| 3400 | 2400MHz | ||||||

| A | 754-pin Lidded OuPGA | ||||||

| E | 1.50V | ||||||

| P | 70 'C | ||||||

| 4 | 512KB | ||||||

| AP | Model 4, Rev.C0, P-state transition support | ||||||

| AR | Model 4, Rev.CG, P-state transition support, Improved CnQ | ||||||

| Brand | Power Limit | Model Number | Package | Operating Voltage | Case Temperature | L2 Cache Size | Part Definition | - |

|---|---|---|---|---|---|---|---|---|

| AM | Mobile AMD Athlon 64 Processor | |||||||

| N | 62W | |||||||

| 2800 | 1600MHz | |||||||

| 3000 | 1800MHz | |||||||

| 3200 | 2000MHz | |||||||

| B | 754-pin Lidless OuPGA | |||||||

| I | 1.40V | |||||||

| X | 95 'C | |||||||

| 5 | 1MB | |||||||

| AP | Model 4, Rev.C0 | |||||||

| AR | Model 4, Rev.CG | |||||||

| A | Desktop Replacement (DTR) | |||||||

| 3000 | 1800MHz | |||||||

| 3200 | 2000MHz | |||||||

| 3400 | 2200MHz | |||||||

| B | 754-pin Lidless OuPGA | |||||||

| E | 1.50V | |||||||

| X | 95 'C | |||||||

| Y | - 'C | |||||||

| 5 | 1MB | |||||||

| AP | Model 4, Rev.C0 | |||||||

| AR | Model 4, Rev.CG | |||||||

| Core | Specs | |

|---|---|---|

| Execution Units | All | 3 x ALU, 3 x AGU, FADD (FADD, MMX, 3DNow!, SSE, SSE2), FMUL (FMUL, MMX, 3DNow!, SSE, SSE2), FMISC, LSU |

| Instruction Decoder | All | up to 3 AMD64, 16-byte read, 3 macro-op early fetch/decode, (n micro-op) per cycle |

| Instruction Dispatch | All | 3 macro-ops |

| Instruction Scheduler | All | 3 x 8-entry int macro-ops (ALU, AGU, (pipe0: Multipler)), 36-entry fp, up to 9 micro-op per cycle |

| Instruction Window | All | 72 in-flight macro-ops |

| Instruction Retirement | All | (3 macro-ops ?) |

| Registers | All | 64-bit mode: 16 architected, n rename GPRs, 8 FPRs, 16 XMM registers |

| Pipeline Stages | All | 12 stage int, 17 stage fp |

| Branch Prediction | All | 16,384-entry Global History Counter table, 2,048-entry branch target buffer, 12-entry return address stack |

| L1-Instruction cache | All | 64KB, 2-way set associative, 64byte-line |

| ITLB | All | Full associative, 32-entry 4KB, 8-entry 2MB/4MB pages |

| L1-Data cache | All | 64KB, 2-way set associative, 64byte-line, 3 clock cycle int latency, dual port |

| DTLB | - | Full associative, 32-entry 4KB, 8-entry 2MB/4MB pages |

| L2 cache | SledgeHammer, ClawHammer | 1MB, 16-way set associative, 64byte-line, exclusive, write back |

| Newcatle, Winchester | 512KB, (n-way set associative), 64byte-line, exclusive, write back | |

| Paris, Dublin | 256KB, (n-way (4?) set associative), 64byte-line, exclusive, write back | |

| L2 ITLB | - | 4-way set associative, 512-entry 4KB pages |

| L2 DTLB | - | 4-way set associative, 512-entry 4KB pages |

| L3 cache | - | - |

| Memory Controller | Athens, SledgeHammer | 128-bit, Registered DIMMs, ECC, ChipKill |

| San Diego, Winchester, (SledgeHammer A64FX), Newcastle | 128-bit, unbuffered DIMMs, ECC | |

| ClawHammer, Paris, Dublin | 64-bit, unbuffered DIMMs, ECC | |

| Multi processing | All | 2-way, 8-way support, Local xAPICs |

| Multi threading | All | Not supported |

| Manufacturing technology | Athens, San Diego, Winchester, Odessa | 90-nano CMOS, 9-layer copper interconnect, PD SOI |

| SledgeHammer, ClawHammer, Newcastle, Paris | 0.13-micron CMOS, n-layer copper interconnect, PD SOI | |

| Transistor count | SledgeHammer | 105.9M |

| ClawHammer | 105.9M | |

| Newcastle | 80-85M (estimated) | |

| Paris | 50-55M (estimated) | |

| Die size | Athens, Troy, Venus | 114sqmm (estimated, official) |

| SledgeHammer, ClawHammer | 193sqmm | |

| Newcastle | About 150sqmm (estimated, official) | |

| Paris | -sqmm | |

| Package, Socket support | SledgeHammer | 940-pin Lidded CuPGA, Ceramic micro PinGridArray, Socket 940, 40x40mm |

| (SledgeHammer A64FX), Newcastle | 939-pin, Socket 939 | |

| ClawHammer | 754-pin Lidded OuPGA, Organic micro PinGridArray, Socket 754 |

レジスタの拡張, 増設

AMDは、既存の32-bitレジスタを拡張する形で64-bitレジスタを実装するとともに、汎用レジスタ (GPR) とSSEレジスタを増設しました。 これにより、これまでは8個だったGPRとSSEレジスタはともに16個となります。64-bit GPRはRAXなどと定義されるほか、 追加されたレジスタはR8-R15、XMM8-XMM15と定義されています。また、アドレス空間が64-bitに対応したことから 命令ポインタも64-bit化されました。ただし、FP/MMXレジスタは変更されず、80-bitのレジスタが8個となっています。

64-bit Long Mode

AMD64アーキテクチャでは、従来の32-bit及び16-bit x86ソフトウェアをそのまま実行できるレガシーモードに加え、 64-bit実行環境を有効にする新たなプロセッサモードが追加されました。新たなプロセッサモードはLong Modeと呼ばれ、 64-bit OS下でLMA (Long Mode Active) と呼ばれるグローバルコントロールビットを操作することで有効になります。 Long Modeはさらに、64-bit ModeとCompatibility Modeの2つのサブモードを備え、 Compatibility Modeでは64-bit OSのもと、既存の32-bit/16-bitアプリケーションを再コンパイルなしで実行可能です。 これらの各モードはLMAのほか、セグメントごとに2-bitのコードセグメントディスクリプタによって指定されます。 各モードにおけるアドレスサイズ、オペランド (データ) サイズは以下のように設定されています。

| Mode | OS Required | Address Size | Operand Size | Register Extensions | GPR Width | |

|---|---|---|---|---|---|---|

| Long Mode | 64-bit Mode | 64-bit OS | 64-bit | 32-bit | yes | 64-bit |

| Compatibility Mode | 32-bit | no | 32-bit | |||

| 16-bit | ||||||

| Legacy Mode | 32/16-bit OS | 32-bit | 32-bit | no | 32-bit | |

| 16-bit | 16-bit | |||||

Source: x86-64 Technology White Paper

レガシーモードでは、プロセッサは従来の32-bit製品と全く同様に振舞います。プロセッサは32-bit x86として動作し、 この場合には64-bit向けに拡張された機能は使用されません。

Compatibility Modeでは、64-bit OSが既存の16-bit及び32-bitアプリケーションに対して、バイナリレベルでの互換性を提供できます。 これにより、64-bit OS環境下において、従来の32-bitアプリケーションなどをそのまま実行することが可能です。Compatibility Modeにおいては、 アプリケーションは仮想アドレス空間の最初の4GBを使用し、レガシーモードと同様、x86命令におけるコードセグメント (CS) ディスクリプタの"D" bitを操作することで 32-bitと16-bitモードを切り替えて実行することが可能です。Compatibility Modeで実行されているアプリケーションに対し、プロセッサは 32-bitまたは16-bitプロテクトモードであるように振る舞います。64-bit長のレジスタや、追加のレジスタなどの拡張機能は使用されません。

既存のアプリケーションがレガシーモードとCompatiblity Modeで実行されるのに対し、AMD64に対応するソフトウェアは 64-bit Modeで実行されます。64-bit Modeの制御はCSディスクリプタに新たに定義した"L" bitを用いて行われ、これによりアプリケーションが 64-bit Modeで実行できるかCompatibility Modeが必要かを判断します。64-bit Modeでは、64-bit仮想アドレス空間 (Opteron/Athlon 64は 48-bit 256TB) のサポート、64-bit長のレジスタと追加されたそれぞれ8個のGPR、SSEレジスタのサポート、64-bit命令ポインタとそれによる 新たなデータアドレッシングモードがサポートされ、コード、データ、スタック領域はフラットなアドレス空間に配置されます。

64-bit Modeでは、デフォルトのアドレスサイズは64-bit、オペランドサイズは32-bitとなっていますが、これらの設定は新たに 用意されたREX命令プリフィックスにより上書きすることができます。このREXプリフィックスはオペランドサイズの指定のほか、 追加されたGPRとSIMDレジスタの指定に用いられます。なお、64-bit ModeではCSを除くセグメントレジスタ、ES、DS、FS、GS、SSは 通常使用されません。

Macro-opsとMicro-ops

OpteronやAthlon 64プロセッサは、K7と同様に2段階の内部命令を用いて実行効率を高めています。 複雑で可変長であるAMD64命令はまず、ある程度簡略化された固定長のmacro-opにデコードされ、 最終的に一つの決まった処理を表すmicro-opに分解されます。ひとつのmacro-opはほとんどの場合、1個の整数または浮動小数点演算と 1個のロードまたはストア、同じアドレスへのロードとストア演算を含み、命令ディスパッチやリタイアメント処理などがmacro-op単位で実行されます。 ひとつのmicro-opは、整数または浮動小数点、ロード、ストア演算のいずれか1個の処理を表し、 プロセッサの実行ユニットにより処理されます。

OpteronなどはAthlon XPと同じく、同時に72個までのmacro-opを管理、実行することができます。 プロセッサはフェッチ-デコードユニットにおいて1サイクルごとに最大3個のmacro-opを出力し、 macro-opはプログラムの順序どおりに命令コントロールユニット (ICU) へ送られます。 ICUは受け取った命令をリオーダバッファで保持するほか、整数スケジューラ及び浮動小数点スケジューラを管理し、macro-opのディスパッチ、 リタイアメント、依存性の解決とりネーム処理、実行リソース管理、割り込み、例外と分岐予測ミスの制御を担当します。ICUではサイクルごとに 3 macro-opsを受け取ることができ、整数及び浮動小数点を合わせて最大72個のmacro-opを制御可能です。ICUでは同時に複数のmacro-opを、 整数及び浮動小数点スケジューラにディスパッチできます。

IPC向上のための強化

OpteronとAthlon 64では、Athlon XPのQuantiSpeedアーキテクチャに対して、Translation-Lookaside Buffer (TLB) や分岐履歴カウンタの 大容量化といった強化も施されています。OpteronとAthlon 64では、L1 ITLBの4-Kbyteページエントリ数がK7の2倍となる32エントリ、 L2 TLBの4-Kbyteページエントリ数も倍の512エントリに増やされました。また、不要なTLBのフラッシュ操作を取り除く、 Flash Filterも導入されています。

分岐予測にはBranch Target address Buffer (BTB)、Global History Bimodal Counter (GHBC) Tableと、 新たに加えられたReturn Address Stack (RAS) を利用します。分岐の予測先アドレスを格納するBTBは2,048エントリ、 2-bitのカウンタによって条件分岐を行うかどうかを示すGHBCは16,384エントリに増やされています。12のエントリが実装されたRASは、 near及びfarコールのあった次のアドレスを復帰先として保持し、復帰の際のペナルティを軽減します。

動作クロックに対するヘッドルームの拡大

Opteronプロセッサの整数パイプラインは、K7プロセッサのものから2ステージ増加し12ステージとなりました。 多くの場合、パイプラインステージが細分化されると各ステージの動作に必要な時間は短縮され、動作クロックを向上させ易くなると言われています。 このため、単純にパイプラインが分割されたとして、さらにバッファの影響や分岐ペナルティなどを無視すれば、Opteronの設計はK7アーキテクチャと比べて 15%ほど高クロック化できるものと考えられそうです。またIBMによれば、SOI (PDSOI) を用いることで従来に比べ20%から30%、 最大35%ほどの高速化が可能になると言われています。Opteronプロセッサの発表時点における Athlon XP 3200+の動作クロックは2.2GHzであるため、あくまで各種ペナルティを無視した場合での初代OpteronやAthlon 64には、 2.8GHz前後までのヘッドルームがあると見ることができそうです。実際、冷却を強化することで2.6GHz前後で動作するとのことです。

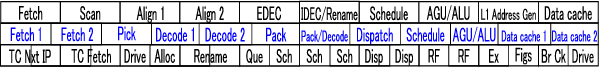

Fig. Integer Pipelines - 上からAthlon XP/MP, Opteron/Athlon 64, Pentium 4/Xeonの分岐予測失敗時のパイプライン

メモリコントローラの統合

Opteronでは、メモリコントローラなどノースブリッジの多くの機能をプロセッサに統合するという、K7からの大きな変更が加えられました。 Opteronではこれまでノースブリッジが担当していたプロセッサバスコントローラに相当するCross Bar (XBAR) と、HyperTransportインターフェース、 メモリコントローラを内蔵しています。これにより、プロセッサからメモリへのアクセスレイテンシを大幅に削減することができ、 実行効率を向上するとされます。 Opteron 244のメモリアクセスレイテンシは、デュアルチャネルDDR333 CL2.5環境下で170クロックほどとされ、ほぼ同環境下における Athlon XP 2500+の約200クロックに対し15%ほど削減されています。

初代Opteronのメモリコントローラは、144-bit (128-bit, 16-bit ECC) DDR333に対応し、帯域幅は最大5.3GB/secでした。 一方、デスクトップ及びモバイル向けのAthlon 64プロセッサはシングルチャネルDDR400のサポート、またOpteron x48以降と Athlon 64 FXはデュアルチャネルDDR400 (Registered ECC) をサポートします。

これらのメモリ対応環境は、2004年3月末にリリースされたSocket 939プラットフォームで一度再整理されました。 Socket 939ではアンバッファドタイプのDIMMを利用するデュアルチャネル環境がサポートされ、939-pinに対応したAthlon 64 FX-53と Athlon 64 3400+以降の製品ではデュアルチャネルDDR400が利用できるようになりました。

なお、AMDではこれらの統合メモリコントローラをDDR-IIに対応させることも可能であると言っているため、後の製品ではそれぞれ、 デュアルチャネルまたはシングルチャネルのDDR-II及びDDRメモリの両方をサポートすると見られています。

AMD Family 6 7th Generation Processors

| Codename | PR/Clock | FSB/PSB | L1/L2 | Ex. | Process | Trs. | Die size | |

|---|---|---|---|---|---|---|---|---|

| Athlon XP | Barton | 3200-2500+ | 400, 333MHz | 64+64/512KB | 3DNow! Pro | 0.13/9 | 54.3M | 101sqmm |

| Thorton | 2400-2000+ | 266MHz | 64+64/256KB | 3DNow! Pro | 0.13/9 | 54.3M | 101sqmm | |

| Thoroughbred | 2800-1600+ | 333, 266MHz | 64+64/256KB | 3DNow! Pro | 0.13/8/9 | 37.6-37.2M | 84-80sqmm | |

| Palomino | 2000-1500+ | 266MHz | 64+64/256KB | 3DNow! Pro | 0.18/7 | 37.5M | 129sqmm | |

| Athlon MP | Barton | 2800+ | 266MHz | 64+64/512KB | 3DNow! Pro | 0.13 | 54.3M | 101sqmm |

| Thoroughbred | 2600-2000+ | 266MHz | 64+64/256KB | 3DNow! Pro | 0.13 | 37.6-37.2M | 84-80sqmm | |

| Palomino | 2100-1500+ 1.2, 1GHz | 266, 200MHz | 64+64/256KB | 3DNow! Pro | 0.18 | 37.5M | 129sqmm | |

| Moible Athlon XP-M | Barton | 2800-2200+ 2000-1900+ LV | 266MHz | 64+64/512KB | 3DNow! Pro | 0.13 | 54.3M | 101sqmm |

| Thoroughbred | 2600-1700+ 1800-1400+ LV | 266MHz | 64+64/256KB | 3DNow! Pro | 0.13 | 37.6-37.2M | 84-80sqmm | |

| Moible Athlon 4 | Palomino | 1.4-0.85GHz | 200MHz | 64+64/256KB | 3DNow! Pro | 0.18 | 37.5M | 129sqmm |

| Athlon | Thunderbird | 1400-750MHz | 266, 200MHz | 64+64/256KB | MMX, 3DNow!+ | 0.18/6 | 37M | 120sqmm |

| K75 | 1000-550MHz | 200MHz | 64+64/(512KB off) | MMX, 3DNow!+ | 0.18/6 | 22M | 102sqmm | |

| K7 | 700-500MHz | 200MHz | 64+64/(512KB off) | MMX, 3DNow!+ | 0.25/6 | 22M | 184sqmm | |

| Duron | Applebred | 1.8-1.4GHz | 266MHz | 64+64/64KB | 3DNow! Pro | 0.13 | 37.6M | 84sqmm |

| Morgan | 1.3-1GHz | 200MHz | 64+64/64KB | 3DNow! Pro | 0.18 | 25.2M | 105sqmm | |

| Spitfire | 950-600MHz | 200MHz | 64+64/64KB | MMX, 3DNow!+ | 0.18 | 25M | 100sqmm | |

| Moible Duron | Morgan | 1.2-0.8GHz | 200MHz | 64+64/64KB | 3DNow! Pro | 0.18 | 25.2M | 105sqmm |

AthlonプロセッサはAMDの第7世代となる製品で、1999年6月に発表されました。Athlonは10ステージ整数/15ステージ 浮動小数点パイプラインを持ち、外部バスはAlpha 21264のEV 6バスを採用しています。K7マイクロアーキテクチャはPentium 4のNetBurstとは対照的に 動作クロック当たりの命令処理能力を高める設計で、改良が加えられたAthlon XP/MP以降ではQuantiSpeedマイクロアーキテクチャと呼ばれています。

- QuantiSpeed architecture - 9命令同時発行、スーパーパイプライン構造を用いたスーパースカラ型x86プロセッサマイクロアーキテクチャ。 クロックサイクルあたりの命令処理数、Instructions Per Cycle (IPC) とともに高クロック動作を可能としました

- 3-way pipelined FPU - x87, MMX, 3DNow!命令を実行可能な3命令同時発行のスーパースカラ、パイプライン型浮動小数点演算ユニット。 Palomino以降ではSSEの実行も可能です

- Hardware data prefetch - 命令実行に必要なデータを先行してメモリからL1キャッシュにロードするデータプリフェッチ機能が、 Palomino以降でハードウェア実装されました

- Exclusive and Speculative Translation Look-aside Buffer - Palomino以降で導入され、TLBに3箇所の改良が加えられたもの。 L1 DTLBのエントリーを32から40に増加、L2 ITLB/L2 DTLBで排他制御方式を採用したほか、TLBエントリーを投機的にロードし キャッシュ領域をあらかじめ確保することが可能です

- Exclusive Cache - Palomino以降導入されたもので、L1/L2キャッシュを排他的に制御する方式。キャッシュ内部でのデータの重複を避けられるため、 キャッシュ全体を有効に利用できます

- EV6 double-pumped FSB - Alpha 21264で使用されているEV6バスを採用、動作クロックに対し倍速でのデータ転送が可能です。 データレートは、200MHz、266MHz、333MHzと400MHzがあります

- MP support - マルチプロセッサ構成が可能で、AMD-760MP系チップセットではデュアルプロセッサがサポートされています。 各プロセッサはチップセットとPoint-to-Point (1対1) で接続されるため、それぞれのプロセッサがバス帯域幅を最大限に利用できます

- Enhanced 3DNow!, 3DNow! Professional - Enhanced 3DNow!では従来の3DNow!に、DSP系命令など24の新命令が追加されました。 また、Palomino以降では単精度浮動小数点SIMDを含む52個のSSE互換命令を追加した、3DNow! Professionalが導入されています

| Architecture Segment | Maximum Power | Model Number | Package Type | Operating Voltage | Die Temperature | Size of L2 Cache | Advanced Front-Side Bus | - |

|---|---|---|---|---|---|---|---|---|

| AXD | AMD Athlon XP Processor Model 10 with QuantiSpeed Architecture for Desktop Products | |||||||

| A | Desktop Power | |||||||

| 3000 | 2100MHz | |||||||

| 3200 | 2200MHz | |||||||

| D | OPGA | |||||||

| K | 1.65V | |||||||

| V | 85 'C | |||||||

| 4 | 512KB | |||||||

| E | 400MHz | |||||||

| 2500 | 1833MHz | |||||||

| 2600 | 1917MHz | |||||||

| 2800 | 2083MHz | |||||||

| 3000 | 2167MHz | |||||||

| D | OPGA | |||||||

| K | 1.65V | |||||||

| V | 85 'C | |||||||

| 4 | 512KB | |||||||

| D | 333MHz | |||||||

| AMS | AMD Athlon MP Processor Model 10 with QuantiSpeed Architecture for Multiprocessor Platforms | |||||||

| N | 60 Watt Processor in Multiprocessor Platform | |||||||

| 2800 | 2133MHz | |||||||

| D | OPGA | |||||||

| U | 1.60V | |||||||

| T | 90 'C | |||||||

| 4 | 512KB | |||||||

| C | 266MHz | |||||||

| AXD | AMD Athlon XP Processor Model 10 with QuantiSpeed Architecture for Desktop Products | |||||||

| C | - | |||||||

| 2000 | 1667MHz | |||||||

| 2200 | 1800MHz | |||||||

| 2400 | 2000MHz | |||||||

| D | OPGA | |||||||

| U | 1.60V | |||||||

| K | 1.65V | |||||||

| T | 90 'C | |||||||

| V | 85 'C | |||||||

| 3 | 256KB | |||||||

| C | 266MHz | |||||||

| AXD | AMD Athlon XP Processor Model 8 with QuantiSpeed Architecture for Desktop Products | |||||||

| A | Desktop Power | |||||||

| 2600 | 2083MHz | |||||||

| 2700 | 2167MHz | |||||||

| 2800 | 2250MHz | |||||||

| D | OPGA | |||||||

| K | 1.65V | |||||||

| V | 85 'C | |||||||

| 3 | 256KB | |||||||

| D | 333MHz | |||||||

| 1600 | 1400MHz | |||||||

| 1700 | 1467MHz | |||||||

| 1800 | 1533MHz | |||||||

| 1900 | 1600MHz | |||||||

| 2000 | 1667MHz | |||||||

| 2100 | 1733MHz | |||||||

| 2200 | 1800MHz | |||||||

| 2400 | 2000MHz | |||||||

| 2600 | 2133MHz | |||||||

| D | OPGA | |||||||

| L | 1.50V | |||||||

| U | 1.60V | |||||||

| K | 1.65V | |||||||

| T | 90 'C | |||||||

| V | 85 'C | |||||||

| 3 | 256KB | |||||||

| C | 266MHz | |||||||

| AMS | AMD Athlon MP Processor Model 8 with QuantiSpeed Architecture for Multiprocessor Platforms | |||||||

| N | 60 Watt Processor in Multiprocessor Platform | |||||||

| 2000 | 1667MHz | |||||||

| 2200 | 1800MHz | |||||||

| 2400 | 2000MHz | |||||||

| 2600 | 2133MHz | |||||||

| D | OPGA | |||||||

| U | 1.60V | |||||||

| K | 1.65V | |||||||

| T | 90 'C | |||||||

| 3 | 256KB | |||||||

| C | 266MHz | |||||||

| Family / Architecture | Generation | Frequency | Package Type | Operating Voltage | Die Temperature | Size of L2 Cache | Advanced Front-Side Bus | - |

| D | AMD Duron Processor Model 8 Architecture | |||||||

| HD | High-Performance Desktop Processor | |||||||

| 1400 | 1400MHz | |||||||

| 1600 | 1600MHz | |||||||

| 1800 | 1800MHz | |||||||

| D | OPGA | |||||||

| L | 1.50V | |||||||

| V | 85 'C | |||||||

| 1 | 64KB | |||||||

| C | 266MHz | |||||||

| Family / Architecture | Generation | Model Number | Package Type | Operating Voltage | Die Temperature | Size of L2 Cache | Max FSB | - |

| A | AMD Athlon XP Processor Model 6 Architecture | |||||||

| X | High-Performance Desktop Processor | |||||||

| 1500 | 1333MHz | |||||||

| 1600 | 1400MHz | |||||||

| 1700 | 1467MHz | |||||||

| 1800 | 1533MHz | |||||||

| 1900 | 1600MHz | |||||||

| 2000 | 1667MHz | |||||||

| 2100 | 1733MHz | |||||||

| D | OPGA | |||||||

| M | 1.75V | |||||||

| T | 90 'C | |||||||

| 3 | 256KB | |||||||

| C | 266MHz | |||||||

| A | AMD Athlon Processor Architecture | |||||||

| MP | High-Performance Processor for Multiprocessing Systems | |||||||

| 1500 | 1333MHz | |||||||

| 1600 | 1400MHz | |||||||

| 1800 | 1533MHz | |||||||

| 1900 | 1600MHz | |||||||

| 2000 | 1667MHz | |||||||

| 2100 | 1733MHz | |||||||

| D | OPGA | |||||||

| M | 1.75V | |||||||

| S | 95 'C | |||||||

| 3 | 256KB | |||||||

| C | 266MHz | |||||||

| A | AMD Athlon Processor Model 4 Architecture | |||||||

| 0900 | 900MHz | |||||||

| 1000 | 1000MHz | |||||||

| 1100 | 1100MHz | |||||||

| 1133 | 1133MHz | |||||||

| 1200 | 1200MHz | |||||||

| 1266 | 1266MHz | |||||||

| 1300 | 1300MHz | |||||||

| 1333 | 1333MHz | |||||||

| 1400 | 1400MHz | |||||||

| A | PGA | |||||||

| M | 1.75V | |||||||

| S | 95 'C | |||||||

| T | 90 'C | |||||||

| 3 | 256KB | |||||||

| B | 200MHz | |||||||

| C | 266MHz | |||||||

AMD Family 5 6th Generation Desktop, Mobile Processors

| Codename | Clock | FSB/PSB | L1/L2 | Ex. | Process | Trs. | Die size | |

|---|---|---|---|---|---|---|---|---|

| K6-III+ | - | 500-450MHz | 100, 95MHz | 32+20+32/256KB | MMX, 3DNow! | 0.18 | - | - |

| K6-III | Sharptooth | 550-400MHz | 100MHz | 32+20+32/256KB | MMX, 3DNow! | 0.25 | 21.3M | 118sqmm |

| K6-2+ | - | 550-450MHz | 100, 97MHz | 32+20+32/128KB | MMX, 3DNow! | 0.18 | - | - |

| K6-2 | Chomper | 500-266MHz | 100, 95, 66MHz | 32+20+32KB/- | MMX, 3DNow! | 0.25 | 9.3M | 81sqmm |

| K6 | - | 300-200MHz | 66MHz | 32+20+32KB/- | MMX | 0.25/5 | 8.8M | 68sqmm |

| K6 | (Nx686) | 233-166MHz | 66MHz | 32+20+32KB/- | MMX | 0.3/5 | 8.8M | 162-157sqmm |